# **SPS-Clock Benutzerhandbuch**

Deutsch

SPS-CLOCK Art.Nr. 9365

11.02.2021

© PI 2021

### **Inhaltsverzeichnis**

## **SPS-Clock**

# 1 Beschreibung

# 2 Systemvorraussetzungen

- 2.1 Software

- 2.2 Hardware

# 3 Anschlussmöglichkeiten

### 4 Installation

4.1 Hardware

## 5 Bedienelemente

- 5.1 Status LEDs

- 5.2 DIP-Schalter

# 6 Konfiguration

- 6.1 Auslesen der Register

- 6.1.1 Registerdaten

6.1.1.1 Statusbits

6.1.1.2 Wochentag

6.2 SPS-Programm

6.2.1 Daten(Arbeits)-DB

6.2.2 OB1

- 6.2.3 Beispiel Aufruf FB für FB99 (FB1)

- 6.2.4 SPS-CLOCK Funktionsbaustein (FB99)

## 7 Technische Daten

7.1 Pinbelegung 15pol. Antennenanschluss

### **SPS-Clock**

## 1 Beschreibung

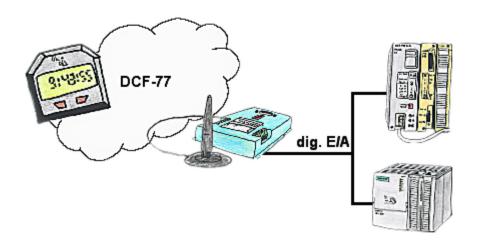

Die SPS-Clock ist ein DCF-Empfänger mit dem über die digitale E/A der SPS die Atomzeit empfangen werden kann. Hierfür benötigen Sie lediglich einige Aus- und Eingänge Ihrer SPS und ein Programm in Ihrer SPS, das die SPS-Clock abfrägt und die Zeit in eine DB hinterlegt. Das Programm wird in diesem Handbuch noch beschrieben.

Folgenden Zeitinformationen stehen zur Verfügung:

- Sekunde

- Minute

- Stunde

- Tag

- Monat

- Jahr (2-Stellig)

- Wochentag (Mo,Di,...)

- Statusbits (DCF-OK,Sommerzeit,Winterzeit,..)

## 2 Systemvorraussetzungen

#### 2.1 Software

• Programm in der SPS zur Abfrage der SPS-Clock (wird im Kapitel "Konfiguration" beschrieben)

#### 2.2 Hardware

- 5 digitale Eingänge an der SPS

- 5 digitale Ausgänge an der SPS

- DCF-Antenne

- optional DCF-Verstärker

- 24V DC Spannungsversorgung

# 3 Anschlussmöglichkeiten

Atomzeit/Funkuhr an SPS-Steuerung

### 4 Installation

#### 4.1 Hardware

Verbindung zur SPS:

Eingänge der SPS-CLOCK mit den digitalen Ausgängen der SPS verbinden Ausgänge des SPS-CLOCK mit den digitalen Eingängen der SPS verbinden SPS-Clock mit +24V Spannung versorgen.

Die Funktionen werden nach Bedarf von der SPS abgerufen und sind im Normalfall (außer bei extrem schnellem Polling der SPS) nicht zeitkritisch. Ein- und Ausgänge sollten bitkompatibel mit der SPS verbunden werden. Bei Verwendung der Beispiel-SPS-Software ist dies unbedingt erforderlich.

Eingänge: Ansteuerung über +24V (Log.1)

kein Signal entspricht 0V (Log.0)

Ausgänge: Bei Log.1 werden +24V durchgeschaltet

Bei Log.0 findet keine Durchschaltung statt

Hinweis: In der aktuellen Version (1.0) der SPS-CLOCK kann auf das Eingangsbit 4 verzichtet werden, da die entsprechenden Register nicht genutzt werden.

### 5 Bedienelemente

#### 5.1 Status LEDs

#### **DCF-Signal LED:**

Grüne LED Aus: kein DCF-Signal wird empfangen

Grüne LED Blinkt: DCF-Signal wird empfangen

#### Mode LED:

Grüne LED Aus:

keine gültige Uhrzeit vorhanden d.h. die Uhr wurde nach dem Einschalten nicht mit einem DCF-Signal synchronisiert

Grüne LED Blinkt:

freilaufende (Quarz) Uhr in Betrieb d.h. das DCF-Signal ist derzeit nicht gültig vorhanden. Interne Uhr wurde 1x synchronisiert und läuft weiter. Statusbits werden nicht ausgegeben.

#### 5V LED:

Grüne LED Aus: Interne 5V werden nicht generiert

Grüne LED An: Interne 5V werden generiert und stehen zur Verfügung

#### **24V LED:**

Grüne LED Aus:

Spannungsversorgung 24V sind nicht am Gerät angeschlossen

Grüne LED An:

Spannungsversorgung 24V sind am Gerät angeschlossen

Sommer/Winterzeit Umstellungen werden nicht vorgenommen.

Grüne LED An:

Im DCF-Betrieb werden alle Daten vom Sender übernommen (Atomzeit). Statusbits werden ausgegeben. Sommer/Winterzeit Umstellungen werden automatisch vorgenommen.

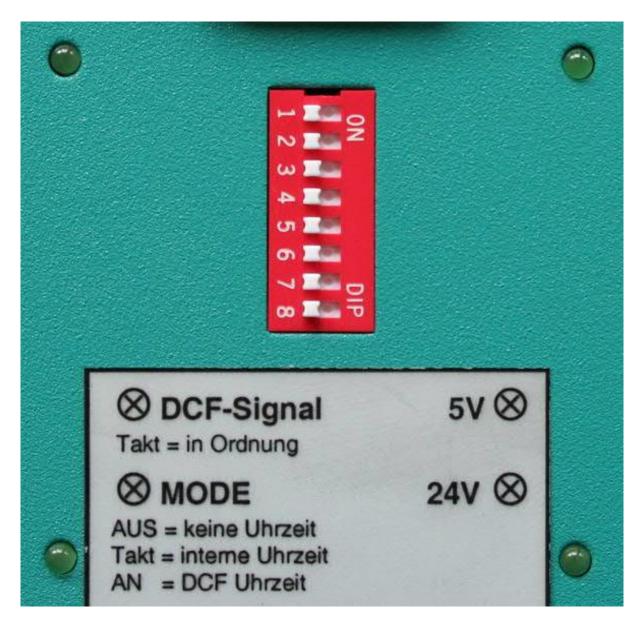

#### 5.2 DIP-Schalter

Die DIP-Schalter sind für zukünftige Verwendung reserviert und müssen im normalen Betrieb auf "0" (OFF) stehen. Sind ein oder mehrere DIP-Schalter auf "1" (ON), kann es zu Fehlfunktionen kommen.

# **6 Konfiguration**

### 6.1 Auslesen der Register

Die Register (gem. Tabelle) werden wie folgt ausgelesen:

- 1. (E) "0" Ausgeben

- 2. (E) '00000' Abfragen

- 3. (N) Register Ausgeben

- 4. (N) ca. 50 ms Warten (hängt von der Peripherie der SPS ab, SPS-CLOCK reagiert nach 2ms)

- 5. (N) Wert Abfragen

- 6. (N) Parity Auswerten

- 7. weitere Abfragen

- (N) = notwendige Schritte für die Abfrage

- (E) = empfohlene Schritte für eine sichere Abfrage

#### 6.1.1 Registerdaten

Die Zeitinformationen können über folgende Register ausgelesen werden:

| Register Nr. | Funktion                    | Wertigkeit |

|--------------|-----------------------------|------------|

| 0            | keine Funktion, Rückmeldung | 00000      |

| 1            | Statusbits                  | PWWWW      |

| 2            | Sekunden (Bit 0-3)          | PWWWW      |

| 3            | Sekunden (Bit 4-7)          | PWWWW      |

| 4            | Minuten (Bit 0-3)           | PWWWW      |

| 5            | Minuten (Bit 4-7)           | PWWWW      |

| 6            | Stunden (Bit 0-3)           | PWWWW      |

| 7            | Stunden (Bit 4-7)           | PWWWW      |

| 8            | Tage (Bit 0-3)              | PWWWW      |

| 9  | Tage (Bit 4-7)   | PWWWW |

|----|------------------|-------|

| 10 | Monate (Bit 0-3) | PWWWW |

| 11 | Monate (Bit 4-7) | PWWWW |

| 12 | Jahre (Bit 0-3)  | PWWWW |

| 13 | Jahre (Bit 4-7)  | PWWWW |

| 14 | Wochentag        | PWWWW |

| 15 | nicht belegt     | 01111 |

| 16 | nicht belegt     |       |

| 17 | nicht belegt     |       |

| 18 | nicht belegt     |       |

| 19 | nicht belegt     |       |

| 20 | nicht belegt     |       |

| 21 | nicht belegt     |       |

| 22 | nicht belegt     |       |

| 23 | nicht belegt     |       |

| 24 | nicht belegt     |       |

| 25 | nicht belegt     |       |

| 26 | nicht belegt     |       |

| 27 | nicht belegt     |       |

| 28 | nicht belegt     |       |

| 29 | nicht belegt     |       |

| 30 | nicht belegt     |       |

| 31 | nicht belegt     |       |

P = Parity-Bit (ungerade)

W = Datenwert

Die Register 2-13 sind geteilte Binärwerte (Bit 7..4 und 3..0)

#### 6.1.1.1 Statusbits

0 = Reserveantenne ist an (am Sender in Mainfingen/Offenbach)

1 = DCF-Betrieb des SPS-CLOCK

2 = UTC + 2h (OEZ/Sommerzeit)

3 = UTC + 1h (MEZ/Winterzeit)

#### 6.1.1.2 Wochentag

- 1 = Montag

- 2 = Dienstag

- 3 = Mittwoch

- 4 = Donnerstag

- 5 = Freitag

### 6.2 SPS-Programm

Das mitgelieferte Testprogramm auf der CD im Verzeichnis \LIZENZ\SPS-CLOCK\ frei parametrierbar und änderbar. Es überträgt zyklisch alle Daten in den Arbeits DB (DW9-16). Sollten Sie nicht alle Daten benötigen so können Sie den Baustein (FB99) leicht auf Ihre Bedürfnisse anpassen.

#### 6.2.1 Daten(Arbeits)-DB

Die Nummer des DB ist vor dem Aufruf des FB99 anzugeben (siehe FB1)

DB 099 Datei: SPSCLKST.S5D LAE=25

```

Datenbaustein fuer SPS-CLOCK

0: KH = 0000:

1: KF = +00000; Intern Schrittkette

2: KF = +00000; Intern Abzurufendes Register

3: KH = 0000:

4: KH = 0000:

5: KH = 0000:

6: KH = 0000;

7: KH = 0000:

8: KH = 0000;

9: KM = 00000000 00000000; Statusbits

10: KF = +00000; Sekunden

11: KF = +00000; Minuten

12: KF = +00000; Stunden

13: KF = +00000; Tage

14: KF = +00000; Monate

15: KF = +00000; Jahre

16: KF = +00000; Wochentag

17: KH = 0000;

18: KH = 0000;

19: KH = 0000;

```

#### 6.2.2 OB1

Der OB1 wird hier nur zum Programmaufruf des Beispiel FB1 benötigt

OB 001 Datei: SPSCLKST.S5D LAE=9

```

Netzwerk 1 von 1

:SPA FB 1

Name :MAIN

:

:BE

```

#### 6.2.3 Beispiel Aufruf FB für FB99 (FB1)

Der FB1 hat folgende Funktionen:

- Übernahme der Eingänge (MB200)

- Vergabe der DB-Nummer (vor FB-Aufruf)

- Parametrierung des FB (TD + TO)

- Übernahme der Ausgänge (MB201)

Die Nummer des FB's ist frei wählbar.

Der Aufruf des FB99 kann durch SPA oder SPB erfolgen.

Ein Mehrfachaufruf im Programm ist möglich.

FB 001 Datei: SPSCLKST.S5D LAE=28

Netzwerk 1 von 1 Name : MAIN

: L EB 0 - Eingaenge von SPS-CLOCK

:T MB 200 in SME

: L KF 99 - Arbeits-DB

: SPA FB 99

Name: SPSCLOCK

TD : T 98 TO : T 99

: L AB 1 - wird Bit 4 nicht genutzt

: L KH 00E0 so kann hier auch 00F0 stehen

: UW

: L MB 201 - Ausgaenge von SME uebergeben

: OW

: T AB 1

: BE

### 6.2.4 SPS-CLOCK Funktionsbaustein (FB99)

#### Der FB99 hat folgende Funktionen:

- Abtasten der einzelnen Register

- Parity Prüfung der Werte

- Übernahme und zusammensetzen der Werte in die Datenworte

Die Nummer des FB's ist frei wählbar.

Im Netzwerk 5 lässt sich der zu übertragende Block leicht beeinflussen (Ober und Untergrenze)

FB 099 Datei: SPSCLKST.S5D LAE=141

Netzwerk 1 von 6 Name : SPSCLOCK

: T MW 240 - Arbeits-DB sichern

: B MW 240 und oeffnen

: A DB 0

: L MB 200 - Nicht fuer SPS-Clock verwendete Bits ausblenden

: L KH 001F

: UW

: T MB 200

: U M 212.0 - VKE 0 Bit erzeugen

: R M 212.0

. \*\*\*

Netzwerk 2 von 6 "Null" und "Fehler"-Signal Auswertung

: L KH 0000 : L MB 200

: !=F

```

: L

KH 000F

: !=F

:=

M 212.2

Netzwerk 3 von 6 Schritt 0 / "0" Ausgeben

: L

DW 1

: L

KF 0

:><F

: SPB

=M001

: L

- Ausgabe "0"

KH 0000

: T

MB 201

: L

KH 0000

- Wenn "Null" als Antwort dann naechster Schritt

:><F

: SPB

=M001

: U

M 212.0

: SE

=TD

- Timer reset

: L

KF 1

: T

DW 1

- naechter schritt

M001: ***

Netzwerk 4 von 6 Schritt 1 / "Register" Ausgeben

: L

DW 1

: L

KF 1

:><F

: SPB

=M001

: L

DW 2

- Ausgabe "Register"

: T

MB 201

: L

KT 0010.0

: SE

=TD

=TD

: UN

- wenn Timer abgelaufen

: SPB

=M001

dann weitere Pruefung

: R

M 212.7

- zu Beginn Parity-Bit ruecksetzen

: L

MB 200

und Eingangsdaten

: T

temporaer uebernehmen

MW 214

: S

und Kennbit setzen

M 214.5

M003: UN

M 215.0

: SPB

=M002

: UN

M 212.7

- Parity in abhaengigkeit vom Datenbit toggeln

:=

M 212.7

M002:L

MW 214

: SRW

: T

MW 214

: UN

M 214.0

- wenn nicht fertig dann Schleife

: SPB

=M003

: UN

M 212.7

- Pruefen ob Parity O.K.

: SPB

und wenn Nein dann Ende

=M004

: L

DW 2

- Registervektor laden

```

"Null"-Signal

:=

M 212.1

```

: T

MW 214

: U

M 215.0

- Bit sichern

:=

M 212.7

: SRW

und durch 2 teilen

1

:1

9

und um 9 erhoehen

: T

MW 214

: U

- welche Tetrade?

M 212.7

: SPB

=M005

: B

MW 214

- Low Tetrade

: L

DR 0

Eintragen

: L

KH 00F0

: UW

: L

MB 200

: SLW

12

: SRW

12

: OW

: B

MW 214

: T

DR 0

: SPA

=M006

M005: B

- High Tetrade

MW 214

: L

DR 0

Eintragen

: L

KH 000F

: UW

: L

MB 200

: SLW

12

: SRW

8

: OW

: B

MW 214

: T

DR 0

M006: L

- Naechstes Register

DW 2

:1

1

: T

DW 2

M004:L

- Fehlerbehandlung

KF 0

: T

DW 1

ruecksprung

M001: ***

Netzwerk 5 von 6 Registerbegrenzung

*** letztes Register (14) ***

: L

KF 14

: L

DW 2

:>=F

: U(

: L

KF 0

01 *** erstes Register +1 (1) ***

:>F

01

01

:)

: SPB

=M001

: L

KF 1

: T

DW 2

M001: ***

```

## 7 Technische Daten

Versorgungsspannung: 24V DC +/- 20%

Leistungsaufnahme: 3 Watt

**Anzeige:** 4 Status-LEDs **Bedienung/Konfiguration:** DIP-Switch

zur AG:

5 x Schraubklemme für E/A-Eingänge

**Schnittstellen:** 5 x Schraubklemme für E/A-Ausgänge

sonstige:

2 x Schraubklemme für 24V/DC Spannungsversorgung

15pol Buchse für DCF77-Antennenanschluss

**Betriebstemperatur:** 0 - 55°C

Gehäuse: pulverbeschichtetes Metallgehäuse mit Montageflansch

**Abmessungen:** 97 x 149 x 36 mm

**Lieferumfang:**

SPS-CLOCK

### 7.1 Pinbelegung 15pol. Antennenanschluss

| Pin Nr. | Kurzform | Bezeichnung                | Richtung |

|---------|----------|----------------------------|----------|

| 1       | GNDA     | Schirm                     | -        |

| 4       | +5V      | +5V Spannungsversorgung    | Ausgang  |

| 5       | GND      | Masse                      | Ausgang  |

| 8       | GNDA     | Schirm                     |          |

| 10      | DCF-IN   | DCF-Signal Empfangsleitung | Eingang  |